ejemplos modo protegido.pdf

Vista previa de texto

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

;

1

6

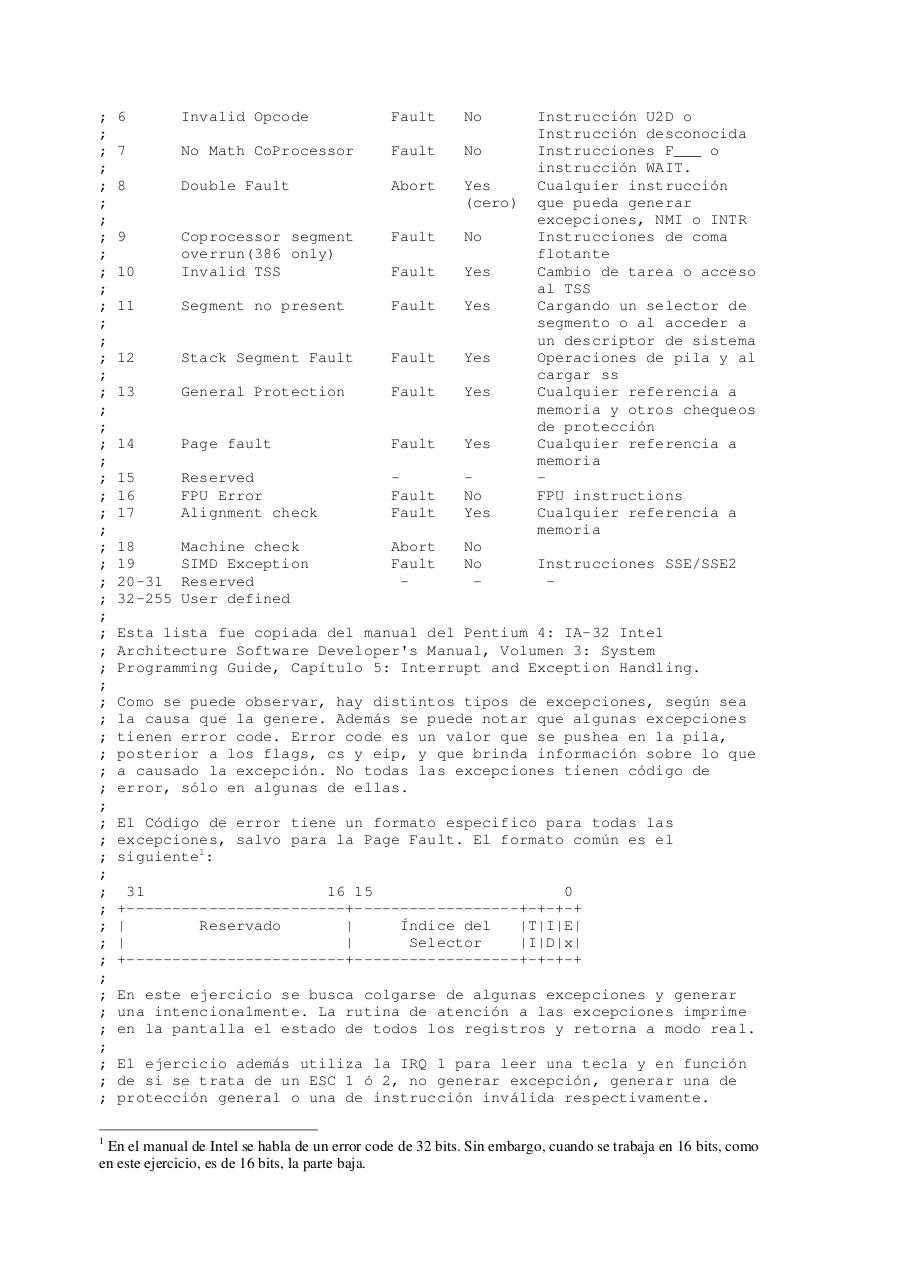

Invalid Opcode

Fault

No

7

No Math CoProcessor

Fault

No

8

Double Fault

Abort

Yes

(cero)

9

Fault

No

10

Coprocessor segment

overrun(386 only)

Invalid TSS

Fault

Yes

11

Segment no present

Fault

Yes

12

Stack Segment Fault

Fault

Yes

13

General Protection

Fault

Yes

14

Page fault

Fault

Yes

15

16

17

Reserved

FPU Error

Alignment check

Fault

Fault

No

Yes

18

19

20-31

32-255

Machine check

SIMD Exception

Reserved

User defined

Abort

Fault

-

No

No

-

Instrucción U2D o

Instrucción desconocida

Instrucciones F___ o

instrucción WAIT.

Cualquier instrucción

que pueda generar

excepciones, NMI o INTR

Instrucciones de coma

flotante

Cambio de tarea o acceso

al TSS

Cargando un selector de

segmento o al acceder a

un descriptor de sistema

Operaciones de pila y al

cargar ss

Cualquier referencia a

memoria y otros chequeos

de protección

Cualquier referencia a

memoria

FPU instructions

Cualquier referencia a

memoria

Instrucciones SSE/SSE2

-

Esta lista fue copiada del manual del Pentium 4: IA-32 Intel

Architecture Software Developer's Manual, Volumen 3: System

Programming Guide, Capítulo 5: Interrupt and Exception Handling.

Como se puede observar, hay distintos tipos de excepciones, según sea

la causa que la genere. Además se puede notar que algunas excepciones

tienen error code. Error code es un valor que se pushea en la pila,

posterior a los flags, cs y eip, y que brinda información sobre lo que

a causado la excepción. No todas las excepciones tienen código de

error, sólo en algunas de ellas.

El Código de error tiene un formato especifico para todas las

excepciones, salvo para la Page Fault. El formato común es el

siguiente1:

31

16 15

0

+------------------------+------------------+-+-+-+

|

Reservado

|

Índice del

|T|I|E|

|

|

Selector

|I|D|x|

+------------------------+------------------+-+-+-+

En este ejercicio se busca colgarse de algunas excepciones y generar

una intencionalmente. La rutina de atención a las excepciones imprime

en la pantalla el estado de todos los registros y retorna a modo real.

El ejercicio además utiliza la IRQ 1 para leer una tecla y en función

de si se trata de un ESC 1 ó 2, no generar excepción, generar una de

protección general o una de instrucción inválida respectivamente.

En el manual de Intel se habla de un error code de 32 bits. Sin embargo, cuando se trabaja en 16 bits, como

en este ejercicio, es de 16 bits, la parte baja.